## **Real Time Instruction Trace**

**Programming Reference**

December 2015

Revision 1.05 Order Number: 332060-004

Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>.

Intel Atom, Intel Core, Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright  $\,^{\hbox{\scriptsize @}}\,$  2015, Intel Corporation. All Rights Reserved.

Revision 1.05 Order Number: 332060-004

## **Table of Contents**

| LIST OF FIGURES                                               | 7  |

|---------------------------------------------------------------|----|

| LIST OF TABLES                                                | 8  |

| REVISION HISTORY                                              | 9  |

| 1 INTRODUCTION                                                | 11 |

| 1.1 Overview                                                  |    |

| 1.2 Availability and Use                                      |    |

| 1.3 FEATURES AND CAPABILITIES                                 |    |

| 1.4 USING THIS SPECIFICATION                                  |    |

| 2 RTIT OPERATIONAL MODEL                                      |    |

|                                                               |    |

| 2.1 RTIT ENABLES                                              |    |

| 2.1.1 Trigger Enable (TriggerEn)2. Context Enable (ContextEn) |    |

| 2.1.3 Filter Enable (FilterEn)                                |    |

| 2.2 Change of Flow Instruction Tracing                        |    |

| 2.2.1 Basic Blocks                                            |    |

| 2.2.2 Direct Transfer COFI                                    | _  |

| 2.2.3 Indirect Transfer COFI                                  |    |

| 2.2.4 Near JMP Indirect and Near Call Indirect                |    |

| 2.2.5 Near RET                                                |    |

| 2.2.6 Far Transfer COFI                                       |    |

| 2.2.7 Flow Control Packet Summary                             | 20 |

| 2.3 Trace Output                                              | 20 |

| 2.3.1 Debug Port                                              | 20 |

| 2.3.2 Output Write Behavior                                   |    |

| 2.4 Trace Filtering                                           |    |

| 2.4.1 Filtering by Current Privilege Level (CPL)              |    |

| 2.4.2 Filter by CR3                                           |    |

| 2.4.3 Filtering by IP                                         |    |

| 2.5 Trace Programming                                         |    |

| 2.5.1 Trace Example                                           |    |

| 2.6 Interaction with Other Components                         |    |

| 2.6.1 System Management Mode2.6.2 Virtual Machine EXtensions  |    |

|                                                               |    |

| 3 CONFIGURATION AND CONTROL                                   | 25 |

| 3.1 ENUMERATION                                               |    |

| 3.2 RTIT ACCESSIBILITY                                        |    |

| 3.3 CPU CONTROL AND MODEL-SPECIFIC REGISTERS                  |    |

| 3.3.1 General MSR notes for RTIT                              |    |

| 3.3.2 RTIT_CTL MSR                                            | 26 |

| 3.3.3 RTIT_STATUS MSR                                               | 29                          |

|---------------------------------------------------------------------|-----------------------------|

| 3.3.4 RTIT_CNTP MSR                                                 |                             |

| 3.3.5 RTIT_EVENTS MSR                                               | 30                          |

| 3.3.6 RTIT_LIPO-3 MSR                                               | 31                          |

| 3.3.7 RTIT_LAST_LIP MSR                                             | 32                          |

| 3.3.8 RTIT_CR3_MATCH MSR                                            | 32                          |

| 3.3.9 RTIT_PKT_CNT MSR                                              |                             |

| 3.3.10 RTIT_BASE_ADDR MSR                                           | 34                          |

| 3.3.11 RTIT_LIMIT_MASK MSR                                          | 34                          |

| 3.3.12 RTIT_OFFSET MSR                                              | 34                          |

| 3.3.13 RTIT_TNT_BUFF MSR                                            |                             |

| 3.3.14 RTIT_LAST_CALL_NLIP MSR                                      | 36                          |

| 4 TRACE PACKETS AND DATA TYPES                                      | 37                          |

| 4.1 Trace Packet Summary                                            | 37                          |

| 4.2 PACKET TYPES                                                    | 38                          |

| 4.2.1 Packet Stream Boundary (PSB)                                  | 38                          |

| 4.2.2 TNT Packet                                                    | 39                          |

| 4.2.3 Target IP Packet                                              | 40                          |

| 4.2.4 Flow Update Packet                                            |                             |

| 4.2.5 Flow Update event: Buffer Overflow                            | 46                          |

| 4.2.6 Flow Update event: Packet Cycle Counter                       |                             |

| 4.2.7 Flow Update event: Packet Generation Enable                   |                             |

| 4.2.8 Flow Update event: Packet Generation Disable                  |                             |

| 4.2.9 Flow Update event: Far Transfer                               |                             |

| 4.2.10 Paging Information Packet (PIP)                              |                             |

| 4.2.11 TraceSTOP Packet                                             |                             |

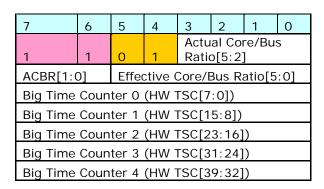

| 4.2.12 Mini Time Counter (MTC) Packet                               |                             |

| 4.2.13 Super Time Sync (STS) Packet                                 |                             |

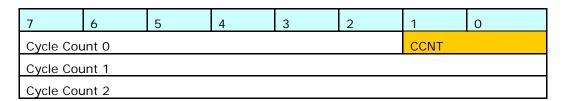

| 4.2.14 Cycle Count Packet                                           |                             |

| 4.2.15 Cycle Accurate Mode                                          |                             |

| 4.3 SYNCHRONOUS PACKETS                                             |                             |

| 4.3.1 Packets sent out in various situations                        |                             |

| 4.3.2 Understanding Entering/Exiting Packet Enabled Region          |                             |

| 4.4 ASYNCHRONOUS PACKET GENERATION                                  |                             |

| APPENDIX A: PROGRAMMING EXAMPLESAPPENDIX B: OPERATION CONSIDERATION |                             |

| 4.1 SLEEP STATES                                                    |                             |

| 4.1.1 C1/Halt/Shutdown sleep state                                  |                             |

| 4.1.2 C2 sleep state                                                |                             |

| 4.1.3 C4 sleep state                                                |                             |

| 4.1.4 C6 and S0i1/S0i2/S0i3 sleep state                             |                             |

| 4.2 Re-Enabling RTIT                                                |                             |

| 4.2.1 Re-Enabling with Same Configuration                           |                             |

| 4.2.2 Re-Enabling with Different Output Region                      |                             |

| 4.2.3 Re-Enabling with Different Traced Region                      |                             |

|                                                                     | Real Time Instruction Trace |

| APPE  | NDIX C: BACKGROUND AND RELATED PROCESSOR MECHANISMS | 64 |

|-------|-----------------------------------------------------|----|

| 4.3   | EXISTING DEBUG AND PERFORMANCE MONITORING           | 64 |

|       | Break point                                         |    |

| 4.5   | LBR/LER                                             | 64 |

| 4.6   | PERFORMANCE MONITORING/PEBS                         | 65 |

| 4.7   | DS FOR BTS/PEBS                                     | 65 |

|       | CR3 STATES                                          |    |

| 4.9   | VIRTUAL MACHINE EXTENSION                           | 66 |

| APPEI | NDIX D: GLOSSARY AND REFERENCE                      | 67 |

|       | GLOSSARY                                            |    |

| 4.11  | Reference Documents                                 | 69 |

| APPEI | NDIX E: ERRATA                                      | 70 |

# List of Figures

| FIGURE 1: REAL TIME INSTRUCTION TRACE OVERVIEW    | 12 |

|---------------------------------------------------|----|

| FIGURE 2: RTIT PACKET HEADER LIST                 | 37 |

| FIGURE 3: PACKET STREAM BOUNDARY                  | 39 |

| FIGURE 4: TAKEN NOT TAKEN PACKET                  | 40 |

| Figure 5: Target IP Packet                        | 40 |

| FIGURE 6: RETURN COMPRESSION WITHOUT NESTED CALLS | 44 |

| FIGURE 7: RETURN COMPRESSION WITH NESTED CALLS    | 45 |

| FIGURE 8: FLOW UPDATE PACKET                      | 46 |

| FIGURE 9: PAGING INFORMATION PACKET               |    |

| FIGURE 10: TRACESTOP PACKET                       |    |

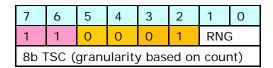

| FIGURE 11: MINI TIME COUNTER PACKET               | 52 |

| FIGURE 12: SUPER TIME SYNCH PACKET                | 53 |

| FIGURE 13: CYCLE COUNT PACKET                     | 53 |

## List of Tables

| 19 |

|----|

| 20 |

| 23 |

| 26 |

| 30 |

| 30 |

| 31 |

| 31 |

| 32 |

| 32 |

| 33 |

| 34 |

| 34 |

| 35 |

| 35 |

| 36 |

| 38 |

| 41 |

| 55 |

| 60 |

| 67 |

| 69 |

|    |

# **Revision History**

| Date          | Revision | Description                                                                             |

|---------------|----------|-----------------------------------------------------------------------------------------|

| February 2015 | 1.00     | Initial Release                                                                         |

| March 2015    | 1.01     | Added read RTIT_CTL MSR requirement                                                     |

| June 2015     | 1.02     | Added erratum E8.                                                                       |

| June 2015     | 1.03     | Fix erroneous text listing RTIT_LIP1 as a limit address and RTIT_LIP2 as a base address |

| August 2015   | 1.04     | Fix intro paragraph Update RTIT_CTL.Dest bit behavior                                   |

| December 2015 | 1.05     | Call out BASE & MASK behavior more clearly Document output write ordering semantics     |

## 1 Introduction

This document describes the programming interface of Real Time Instruction Trace (RTIT), including trace configuration options and trace output. RTIT is available only on 3rd generation Intel<sup>®</sup> Atom<sup>TM</sup> processor (code named Silvermont)-based and 4th generation Intel Atom processor (code named Airmont)-based products, see  $\underline{1.2}$  for details on which products are supported.

### 1.1 Overview

In current Intel® architecture, Last Branch Record (LBR) and Branch Trace Store (BTS) features allow observance of internal CPU program flow. Branch information, i.e., the source and destination instruction pointers, can be stored in a hardware stack, or written to memory via processor support. Debug software can reproduce program flow based on the branch addresses and source code. However, the overhead of using BTS is very significant, while LBR only captures the last several branches only, both limitations that prohibit their use in real-time application debugging.

Real Time Instruction Trace (RTIT) works on the same principle as BTS and LBR. It operates in parallel to the primary processor pipeline and uses a separate output streaming mechanism that is external to the processor. This eliminates the limitations of existing debug mechanisms and allows continuous and efficient runtime application debugging.

RTIT encodes and compresses program flow information, such as branch targets, branch taken/not taken indications, and carries them to the memory subsystem in real time, avoiding the use of any processor assist methods. The memory subsystem then forwards the RTIT data out to external receivers for debug software to post-process and reconstruct program flow.

Revision 1.05 Order Number: 332060-004

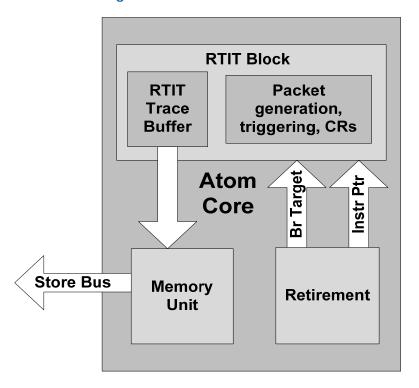

Figure 1: Real Time Instruction Trace Overview

Figure 1 shows how the RTIT logic fits into a System on a Chip (SOC) system. The RTIT Block monitors the Intel<sup>®</sup> Atom<sup>™</sup> processors core retirement pipeline and generates trace packets upon retiring change of program flow instructions of interest. RTIT stores the traces in a trace buffer until they are stored out to memory or to pins.

## 1.2 Availability and Use

The RTIT programming interface is available as model-specific feature only on certain Intel<sup>®</sup> Atom<sup>™</sup> processors listed below. The definitions and usages of RTIT described in this document apply to those processors models, in some cases, specific stepping. Intel<sup>®</sup> Atom<sup>™</sup> processors supported by Family/Model/Steppings are as follows:

#### Silvermont Microarchitecture:

- 0x6/0x37/0x8

- 0x6/0x5d/0x0

- 0x6/0x5d/0x1

- 0x6/0x4a/0x8

- 0x6/0x4d/0x8

- 0x6/0x5a/0x0

#### <u>Airmont Microarchitecture:</u>

0x6/0x4c/0x3

## 1.3 Features and Capabilities

RTIT generates a variety of packets that, along with the sources of a program, can be used to produce an exact execution trace. The packets record information such as Linear and Target Instruction Pointers (LIP and TIP) and direction of conditional branches within a contiguous code region (basic blocks). In addition the packets record other contextual, timing, and bookkeeping information to enable both functional and performance debugging of applications.

RTIT has several control and filtering capabilities to customize and compress the tracing information collected and to append other processor state and timing information to enable debugging.

- **Programmable address comparison registers** can be used to qualify RTIT output by specifying different IP ranges and masks.

- CPL and CR3 filtering modes allow filtering based on CPL execution mode (USER ring-3 or SUP ring-0) and on CR3 values.

When enabled and appropriately configured, RTIT will collect and generate the following types of trace information:

<u>Packet stream Boundary (PSB) packets</u>: The PSB acts as a 'heartbeat' that is generated at regular intervals (e.g., every 8K trace packet bytes). PSB is a unique pattern, which allows decodes to sync into a RTIT byte stream.

<u>Taken Not Taken (TNT) packets:</u> TNT packets track the "direction" of direct conditional branch (i.e., taken or not taken). TNT packets are 1 byte, including the header. 1 to 6 TNT (Taken-Not-Taken indications) can be packed in one TNT packet with a '1 signifying a taken branch and a '0 signifying a not-taken branch that fell through to next instruction.

<u>Target IP (TIP) packets:</u> TIP packets record the target IP of indirect branches, exceptions, and interrupt handlers. Up to 48 bits of IP can be stored, and the most significant bits that are identical to the branch LIP or are entirely 'Os can be suppressed to reduce the packet size.

<u>Flow Update (FUP) packets:</u> FUP packets record a variety of contextual information to aid in decoding the trace output. These include:

- **Buffer Overflow packets (FUP.OVF)** indicate that the RTIT internal buffer is full and that packets are no longer being generated.

- **Periodic Cycle Counter (FUP.PCC)** is periodically generated based on increments in a cycle counter.

- Packet Generation Enable (FUP.PGE) packets are generated when RTIT is enabled, or if the execution enters a region that is configured for RTIT tracing.

- Packet Generation Disable (FUP.PGD) packets are generated when RTIT transitions from a

packet generating mode into a disabled mode due to filtering criteria not being met, or

disabling RTIT.

- Far Transfer (FUP.FAR) packets are generated after a far transfer and will include an address indicating where the transfer came from. It is usually generated with TIP, and appears before the corresponding TIP in the trace output.

Paging Information Packet (PIP): PIP record any modifications to the CR3 register while memory paging is enabled. This, along with process page information from the operating system, allows the debugger to attribute linear addresses to their correct application source line.

Trace STOP (STOP) packets: STOP packets are generated when the current IP matches a region specified by the 'TraceStop' filter.

Super Time Sync (STS) packets: STS packets are generated upon several processor frequency, power, and other state global events. They will contain the value in the processor's HW TSC, and along with MTC are used by the debug analyzer to synchronize the traces with wall time.

Mini Time Counter (MTC) packets: MTC packets can be generated periodically based on the processor's HW TSC, and along with STS are used by the debug analyzer to synchronize the traces with wall time.

Cycle Count Packet (CCP): CCP packets contain the incremental number of core cycles since the previous CCP, and are generated after certain other trace packets based on the configuration of the cycle accurate mode.

## 1.4 Using This Specification

Chapter 1: Introduction gives an introduction to RTIT, where it is available, and describes the features and capabilities to customize tracing information based on user needs.

Chapter 2: RTIT Operational Model provides additional details about RTIT including the enabling and filtering, and describes essential program flow concepts that form the basis of the RTIT tracing model.

Chapter 3: Configuration and Control details the various mechanisms necessary for configuring, enabling, controlling, and collecting RTIT data in an operating system or Virtual Machine Monitor.

Chapter 4: Trace Packets and Data Types details the packets generated by RTIT to assist developers in decoding RTIT data and utilizing it to recreate an application execution trace.

## 2 RTIT Operational Model

This chapter describes the overall RTIT mechanism and explains essential concepts used throughout the remainder of the document. Reading this chapter will provide a basic understanding of how RTIT operates, and a detailed understanding of the various features and capabilities offered by RTIT.

This chapter is organized as follows: Section <u>2.1</u> explains the different circumstances and context during which RTIT will be generating trace packets. Section <u>2.2</u> explains the notions of flow control that are used by the RTIT mechanism to produce an execution trace. Section <u>2.3</u> describes the primary mechanism for streaming RTIT packets. Section <u>2.4</u> describes the different filters that can be used to restrict which execution streams are traced by RTIT. Section <u>2.5</u> gives an overall view of RTIT programming and provides an example of such programming. Finally, Section <u>2.6</u> describes how RTIT will behave while the processor is in non-standard execution modes.

### 2.1 RTIT Enables

RTIT has a variety of enables and disables that interact to ultimately decide if a packet should be generated. This state is referred to as Packet Enable and is synonymous with PacketGenEnable, Packet Generation Enable or PacketEn.

When Packet Enable is set, we are in the code that RTIT is monitoring and packets are being generated to log what is being executed. PacketEn is composed of 4 other states according to this relationship:

PacketEn = TriggerEn && ContextEn && FilterEn

Each of these states is detailed in the following subsections.

## 2.1.1 Trigger Enable (TriggerEn)

TriggerEn (Trigger Enable) is the primary indicator that RTIT is active. TriggerEn is defined using two fields:

TriggerEn = (RTIT\_CTL[Trace\_En] AND RTIT\_CTL[TraceActive]).

Software can get the current TriggerEn value by reading the RTIT\_STATUS[TriggerEn] MSR bit. When TriggerEn is clear, RTIT is inactive and no packets are generated.

#### 2.1.2 Context Enable (ContextEn)

Context Enable (ContextEn) indicates that the processor is in the state that RTIT is configured to watch. For example, if RTIT is configured to watch only application code (RTIT\_CTL[OS]=0), then ContextEn will be 0 when the CPU is in CPLO.

15

Software can get the current ContextEn value by reading the RTIT\_STATUS[ContextEn] MSR bit. ContextEn is defined as follows:

```

ContextEn = !(

(RTIT_CTL[OS]=0 AND CPL=0) OR

(RTIT_CTL[USER]=0 AND CPL=1,2,3) OR

(RTIT_CTL[CR3En]=1 AND RTIT_CR3_MATCH!=CR3) OR

(In SMM mode) OR

(In VMX mode))

```

When ContextEn is cleared, many packets are not generated, including all branch packets. However, some packets, such as the MTC, may still be generated while ContextEn is clear.

## 2.1.3 Filter Enable (FilterEn)

Filter Enable indicates that the CPU Instruction Pointer (IP) is within the range of the IPs that RTIT is configured to watch. See section 2.4.3 for details on IP filtering.

Software can get the state of Filter Enable by an MSR read of RTIT\_STATUS[FilterEn].

Filter enable is only 'usually' correct because it may be incorrect if the RANGEO/1 ranges are not set up correctly. It is also frozen when either Trace\_En or ContextEn are 0.

## 2.2 Change of Flow Instruction Tracing

#### 2.2.1 Basic Blocks

A program block is a section of code where no jumps or branches occur. The IPs in this block of code need not be traced, as the CPU will execute them from start until end without redirecting code flow. Instructions such as branches, and external events such as exceptions or interrupts, can change the program flow. These instructions and events that change program flow are called COFI (Change of Flow Instructions). The program block is divided into these three categories:

- Direct transfer COFI.

- Indirect transfer COFI.

- Far transfer COFI.

The following subsections describe the IA architecture COFI events that result in trace packet generation. For detailed description of the instructions, please refer to "Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 2A/2B: Instruction Set Reference."

#### 2.2.2 Direct Transfer COFI

These types of instructions include conditional jumps, and jumps that are to a Linear Instruction Pointer (LIP) that is embedded in the instruction bytes. It is not necessary to output the LIP of the destination address since it can be obtained through the source code. It is only necessary to indicate whether the conditional branch is taken or not.

#### 2.2.2.1 Jump if condition is met (Jcc) and LOOP

To track this type of instruction, RTIT uses a single bit of TAKEN or NOT TAKEN (TNT) to indicate the program flow after the instruction. When the condition check is evaluated to true (i.e., the branch will

be taken), the processor IP will update to the target IP specified in the instruction. This is encoded as TAKEN in the RTIT TNT packet; otherwise, the program will simply go to the next LIP, and is encoded in the TNT as NOT TAKEN.

Jcc and LOOP can be traced with TNT bits. To improve the trace packet output efficiency, RTIT will compact several TNT bits in a single packet. This can output up to 6 consecutive TNT bits in one TNT packet.

## 2.2.2.2 Unconditional Direct Jumps

There is no RTIT output for direct unconditional jumps (like JMP near relative or CALL near relative) since they can be directly inferred from the application assembly. Direct unconditional jumps do not generate a TNT bit or a Target IP packet.

### 2.2.3 Indirect Transfer COFI

Indirect transfer instructions involve updating the LIP from a register or memory location. Since the register or memory contents can vary at any time during execution, there is no way to know the target of the indirect transfer until the register or memory contents are read. As a result, the disassembled code cannot be used alone to determine the target of a COFI. Therefore, RTIT must send out the destination LIP in the trace packet for debug software to determine the target address of the COFI.

Indirect Transfer instructions will generate a Target IP packet (TIP) which contains the target linear address of the branch or the new instruction pointer.

#### 2.2.4 Near JMP Indirect and Near Call Indirect

As previously mentioned, the target of an indirect COFI resides in the contents of either a register or memory location. Therefore RTIT must expose this target address to the debug software in order to determine the target of the COFI.

#### 2.2.5 Near RET

When a CALL instruction executes, it pushes the address of the next instruction following the CALL onto the stack. Upon completion of the call procedure, the RET instruction is often used to pop the return address off of the call stack and redirect code flow back to the instruction following the call.

A RET instruction simply transfers program flow to the address it popped off the stack. Because it is possible for software to change the Extended IP (EIP) on the stack within the call procedure prior to executing the RET instruction, the debug software can be misled if it always assumes code flow will return to the instruction following the last call. Therefore, even for near RET, a Target IP Packet is sent to handle this case.

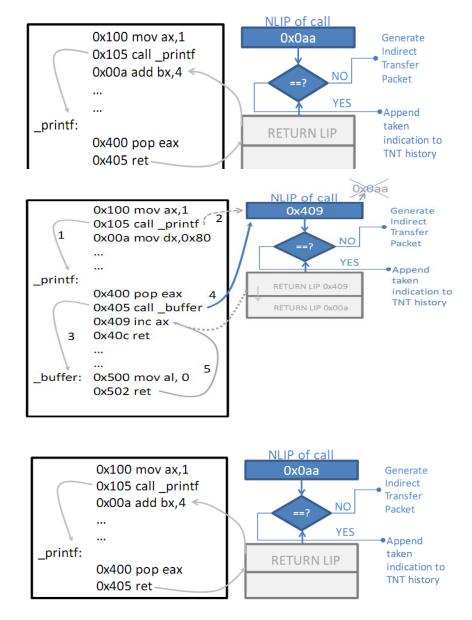

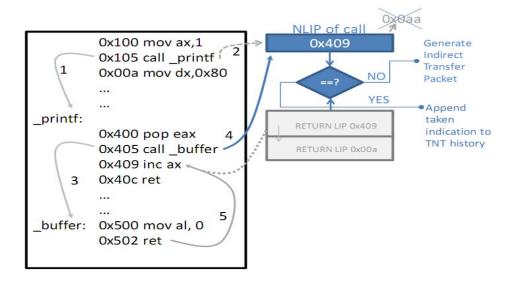

A special case is applied if the target of the RET matches the Next LIP (NLIP) of the last CALL instruction. Then only a single TNT bit of "Taken" is generated instead of a Target IP Packet.

## 2.2.6 Far Transfer COFI

All operations that change the instruction pointer which are not near jumps are "far transfers". This includes exceptions, interrupts, traps, and instructions that do far transfers (i.e. SYSENTER, SYSEXIT, SYSCALL, SYSRET, software interrupts, far jump, far call, far RET and IRET).

Far transfers that produce RTIT packets will produce a Flow Update Packet of type Far Transfer (FUP.FAR) followed by a Target IP packet (TIP); unless the far transfer also jumps out of the filtered region while keeping ContextEn==1. A far transfer that causes FilterEn to become 0 but keeps ContextEn at 1 will produce Flow Update packet of type PacketGenerationDisable (FUP.PGD instead of FUP.FAR) followed by a Target IP packet. This is a form of compression and simplifies the hardware.

The following table indicates exactly which LIP will be included in the FUP.FAR or FUP.PGD generated by a far transfer.

**Table 1: IP Type in Various Packets**

| Event                                                                             | Flow Update LIP                                                                                              | Note                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Far CALL/JUMP<br>SYSENTER/SYSEXIT<br>SYSCALL/SYSRET<br>Far RET<br>IRET            | Address of next instruction<br>(Next Linear Instruction<br>Pointer)                                          | This does not match LBR FROM field, which records the address of the branch instruction. RTIT trace analysis does not need this flow update packet since it should know where the branch is, but it would require more hardware to suppress it. |

| External Interrupt<br>NMI/SMI<br>Traps<br>Machine Check (trap-<br>like)           | Address of next instruction (NLIP) that would have been executed                                             | This matches the LBR FROM field value and also the EIP value which is saved onto the stack. Remember that LBRs are linear (not effective) addresses for Intel <sup>®</sup> Atom <sup>™</sup> processors.                                        |

| INIT/SIPI                                                                         | Address of next instruction (NLIP) that would have been executed                                             | Lower certainty on INIT and SIPI behavior.<br>Not important to RTIT usage.                                                                                                                                                                      |

| (FUP.PGD only) Walking out or region Non-far transfer that changes ContextEn to 0 | Address of next instruction (NLIP) that would have been executed                                             | LBRs have no such concept.                                                                                                                                                                                                                      |

| (FUP.PGD only)<br>Near jump out of region                                         | Address of next instruction (NLIP) that would have been executed                                             | This does not match the LBR field, which would record the address of the branch instruction.                                                                                                                                                    |

| Exceptions/Faults<br>Machine check (fault-<br>like)                               | Address of the instruction which took the exception/fault (Current LIP)                                      | This matches the LBR FROM field value and also the EIP value which is saved onto the stack.                                                                                                                                                     |

| Asynchronous Flow Update Packet Buffer Overflow Periodic Cycle Counter            | Address of next instruction (NLIP/BLIP) that will execute after the instruction where the condition occurred | LBRs have no such concept.                                                                                                                                                                                                                      |

| PacketEn goes from 0 to 1 (includes VM-entry and RSM)                             | Address of where we entered region (BLIP or NLIP)                                                            | LBRs have no such concept.                                                                                                                                                                                                                      |

| VM-exit                                                                           | Address that is saved into the VMCS as guest RIP                                                             | LBRs have no such concept.                                                                                                                                                                                                                      |

## 2.2.7 Flow Control Packet Summary

The following table summarized the trace packets as per each instruction

Table 2: Classifying branches and COFI

| Instruction                                                           | Packet      | Note                                                                                   |

|-----------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------|

| Jcc/LOOP                                                              | TNT         | Branch taken/not taken packet.                                                         |

| Near Jump (indirect)<br>Near Call (indirect)<br>Near RET              | Target IP   | Branch destination LIP(BLIP) is sent in target IP Packet.                              |

| Far Transfers, including:<br>Far Jump/CALL                            | Flow Update | LIP before the far transfer. Same as recorded in LBRs (or would be pushed onto stack). |

| Far RET/IRET Exception/Interrupt/Trap SYSENTER/SYSEXIT SYSCALL/SYSRET | Target IP   | Branch destination LIP(BLIP) is sent in target IP Packet.                              |

## 2.3 Trace Output

RTIT packet data is written by the CPU to the memory subsystem. RTIT writes use the USWC memory type, regardless of what is specified by the MTRRs. The use of platform physical addressing means that RTIT writes are not affected by page tables or EPT tables.

The RTIT output destination is specified by writing a platform physical address to the RTIT\_BASE\_ADDR MSR to serve as the destination base, and a mask value to the RTIT\_LIMIT\_MASK MSR to dictate the size of the region. The RTIT\_BASE\_ADDR value should be aligned to the size of the output region (RTIT\_LIMIT\_MASK+1), as the base value used will be RTIT\_BASE\_ADDR & ~RTIT\_LIMIT\_MASK.

The RTIT\_OFFSET MSR holds the offset into the region specified by RTIT\_BASE\_ADDR and RTIT\_LIMIT\_MASK. Thus the physical address to which RTIT stores are directed is computed as follows:

RTIT\_BASE\_ADDR + (RTIT\_OFFSET & RTIT\_LIMIT\_MASK)

Note that the buffer is treated as circular, and hence once the offset value reaches the mask value, writes will wrap around and write at offset 0 again.

## 2.3.1 Debug Port

In order to send RTIT output to a debug port, the platform-specific memory-mapped I/O (MMIO) address for the port of interest should be written to the RTIT\_BASE\_ADDR MSR, with the RTIT\_LIMIT\_MASK value set to match the size of the desired MMIO range. As described above, RTIT output will be written to this address range in a circular fashion.

Please see SoC documentation to determine which debug port options exist for your platform.

## 2.3.2 Output Write Behavior

RTIT output writes pass through the memory subsystem, and like other memory writes RTIT output is written out in 64 byte lines. In some cases, it is possible to observe partial line writes of RTIT data. This can result from enabling trace with an unaligned RTIT\_OFFSET value (which would cause output to begin in the middle of the line), or from a fencing operation causing a line to be written out before it is filled (which would cause the RTIT bytes to cease before the end of the line). RTIT disable or bus locks are examples of operations that could prematurely flush an RTIT line. The implication is that it is possible to see individual RTIT writes that may include invalid bytes at the beginning and/or at the end of the line. However, as long as RTIT\_OFFSET is not manipulated by software, the resulting output will be contiguous and non-overlapping.

USWC writes, like those employed by RTIT, are not strongly ordered, and thus it is possible (though rare) to observe a younger line written to its endpoint before an older line. When an RTIT drain is executed (e.g., on write to RTIT\_CTL), all RTIT writes are fenced, and hence any re-ordering should have no effect on the resulting output bytes. For this reason it is recommended that collectors always disable RTIT before collecting trace output. If RTIT output is examined or collected before a drain is executed, as is typical when writes are directed to a trace hub or arbiter, the collector may need to be able to re-order any out-of-order writes. In such a case, please refer to the corresponding spec for the trace hub employed to determine the possibility of receiving out-of-order RTIT writes from the CPU.

When out-of-order RTIT writes are exposed, the degree of software re-ordering required is limited. Let us enumerate the lines comprising the output region as A, B, ..., n, such that line A is the first 64-byte line in the buffer, and n is the last. Software can discern which line has been received by examining the address bits offset from the output base address in RTIT\_OUTPUT\_BASE. In this scenario, we'll define an "iteration" as the sequence of writes to A..n before the output wraps back to A. Using line B as an example, it is possible that, before a given iteration of B is seen, younger lines C..n from the same iteration may be seen. It is even possible that the next iteration of A could be seen before B. However, it is not possible to first see a younger iteration of B, nor any still younger lines (e.g., next iterations of C..n).

## 2.4 Trace Filtering

## 2.4.1 Filtering by Current Privilege Level (CPL)

RTIT provides the ability to specify whether tracing occurs when code is executing in CPLO or not. RTIT can be configured to be enabled only when in CPLO, when in CPL1/2/3, or at all CPLs. When in a non-enabled CPL, the Context Enable is cleared.

The CPL value that is used to determine the RTIT Context Enable is read after instruction retirement. This means that speculative CPL changed will not affect the RTIT state. For example, a page fault which triggers a change of CPL from 3 to 0 will not send out a TIP packet if RTIT is configured to only monitor CPL 1/2/3. A FUP packet will still be generated to indicate a traced region was left.

## 2.4.2 Filter by CR3

To reduce the total trace size, it is important to be able to trace a single application without requiring software intervention every time applications are switched.

Since CR3 (the page table pointer) is the primary piece of CPU state that indicates which application is running, RTIT can enable or disable tracing depending on the CR3 value. This is done through the CR3 filtering/matching feature.

If the RTIT user desires to only trace a single CR3, then they can program that CR3 value into RTIT\_CR3\_MATCH MSR and set RTIT\_CTL.CR3En. When the CR3 value does not match that in RTIT\_CR3\_MATCH, the processor will disable RTIT (ContextEn forced to 0). When the CR3 value does match of RTIT\_CR3\_MATCH, then the processor will stop disabling RTIT because of the CR3 value (although it could remain disabled due to other filters like CPL). If RTIT\_CTL.CR3En is 0, then all CR3s are monitored (RTIT tracing is not disabled by the CR3 value).

The Paging Information Packet is sent out in various situations to explain to the analyzer which app is being executed. When a non-paging mode is entered (CR0.PG is cleared), a paging information packet is generated. This will not affect the current CR3 filtering because it is not a direct change in the value of CR3.

OS-specific techniques will need to be used to discover the CR3 value that corresponds to a particular already-running application. If the application can only be started when RTIT is already running, other techniques (like OS debug hooks, OS modification or using a special driver) may need to be used to discover the CR3 value and subsequently update the RTIT CR3 filters.

## 2.4.3 Filtering by IP

RTIT can be configured to enable control flow packet generation only when the CPU is executing code within certain IP ranges. This is controlled with FilterEn, which, if IP filtering is enabled, is set only when the IP is in one of the ranges specified by SW. If the IP is outside of these ranges, then FilterEn is cleared and no control flow packets are enabled.

IP filtering is enabled using the RTIT\_EVENTS MSR. This MSR configures use of the RTIT\_LIP[0123] MSRs, which are used to define the base and limit of the range(s) in which tracing is enabled. Current RTIT implementations have 2 such ranges, known as RANGE0 and RANGE1. RANGE0 is defined by [RTIT\_LIP0..RTIT\_LIP2-1], while RANGE1 is defined by [RTIT\_LIP1..RTIT\_LIP3-1].

EventIDs are used for IP filtering, and for TraceStop. RTIT\_EVENTS[Filter Event ID] and RTIT\_EVENTS[Stop Trace Event ID] are programmed with event ID encodings, which are details in section 3.3.5. Note that the Filter event ID and TraceStop event ID are two separate fields, and thus different conditions can cause those actions.

To save power, the comparison of the IP to the RANGEO/1 ranges is done only when RTIT\_CTL[Trace\_En] is set. This means that the FilterEn value will not be changed by the IP when Trace\_En is cleared. This means that leaving Trace\_En set but disabling RTIT by having Trace\_Active cleared consumes more power than if Trace\_En was also cleared.

It is important to note that, though no control flow packets are generated from outside of the IP filter ranges, some packets can be generated at this time. Periodic packets, such as MTC and PSB, can still be generated when FilterEn is 0.

## 2.5 Trace Programming

RTIT provides the end-user with a highly configurable set of tracing capabilities and programmable events for both performance analysis and debug. RTIT is configured through code execution via the WRMSR and RDMSR instructions.

## 2.5.1 Trace Example

If RTIT was programmed to trace all CPLs and the address filters were restricting the IP range to instruction between 0x100-0x110, then the following RTIT packets would be generated:

CLIP NI IP Step Instruction RTIT output 1 0x020 0x023 Jmp to 102 1. FUP.PacketGenEnable of 102 (BLIP) 2 0x100 0x102 Xor eax, eax Nothina 3 0x102 0x105 Far JMP to 983 1. FUP.PacketGenDisable of 105 (NLIP) 2. TIP of 983 (BLIP) 4 0x983 0x985 Far JMP to 10E 1. FUP.PacketGenEnabled of 10E (BLIP) 5 0x10E 0x113 1. FUP.PacketGenDisabled of 10E (NLIP) Divide that causes Divide by 0 fault 2. TIP of 345 (BLIP) Fault handler at 345 6 0x345 0x348 Add (first instr of **Nothing** fault handler 7 348 34c POP ret address to Nothing RAX 8 34c 350 Modify RAX to point Nothing to 113

Nothing

Nothing (since 113 is outside of range)

**Table 3: RTIT Trace Example**

## 2.6 Interaction with Other Components

PUSH new ret addr

of 113 onto stack

IRET to 113

## 2.6.1 System Management Mode

RTIT is always disabled during System Management Mode (SMM). Whenever a System Management Interrupt (SMI) occurs, the CPU will set an internal "We are in SMM mode" bit that will force ContextEn to become 0 if it was not already 0. If this caused PacketEn to transition from 1 to 0, then a FUP.PGD will be sent out with the address of the next instruction that would have executed had the SMI not occurred. A TIP packet is never generated on an SMI since the SMI results in ContextEn is 0 (and any operation that disabled ContextEn does not send out a TIP).

Whenever an RSM occurs, the CPU will clear the internal "We are in SMM mode" bit, which will thus stop forcing ContextEn to 0. In the normal case, this will cause ContextEn to return to the value that it was before the SMI. If that causes PacketEn to transition from 0 to 1, then a FUP.PGE will be generated with the address of the target of the RSM (the next instruction to execute after the RSM). If the SMM return address was not modified, this will usually be the same address as was seen on the FUP.PGD generated on the preceding SMI.

9

10

350

353

353

357

As discussed earlier, the software SMM handler could do various things that would cause the RSM to return to a different instruction or mode than was executing before the SMI. For example, it could change the return address to be outside of the filtered region when it was inside the filtered region before the SMI. Or it could change the CR3 value.

The RSM simply clears the "We are in SMM mode" bit that was forcing ContextEn to 0. FilterEnable and the CPL will also be re-evaluated automatically based on the processor settings mode that the RSM is loading (whether it was the same as that before the SMI or not).

The RSM re-evaluates whether the CR3 matches the RTIT\_CR3\_MATCH MSR, and determines the SMI does not. Therefore, it is not needed on the SMI since the SMI will clear ContextEn and it cannot be set until the RSM occurs.

#### 2.6.2 Virtual Machine EXtensions

RTIT is always disabled in Virtual Machine EXtensions (VMX) host mode (this mode is also referred to as VMM, root mode, or the hypervisor).

Whenever a VM exit occurs, the CPU will set an internal "We are in VMM mode" bit that will force ContextEn to become 0 if it was not already 0. If this caused PacketEn to transition from 1 to 0, then a FUP.PGD will be sent out with the address that is saved into the VMCS as the RIP. A TIP packet is never generated on a VM exit since the VM exit results in ContextEn of 0 (and any operation that disabled ContextEn does not send out a TIP).

Whenever a VM entry occurs, the CPU will clear the internal "We are in VMM mode" bit, which will thus stop forcing ContextEn to 0. In the normal case, this will cause ContextEn to return to the value that it was before the VM exit. If that causes PacketEn to transition from 0 to 1, then a FUP.PGE will be generated with the address of the target of the VM entry. If the VMCS guest RIP field was not modified, this will usually be the same address as was seen on the FUP.PGE generated on the preceding VM exit. VM entry will re-evaluate whether CR3 matches RTIT\_CR3\_MATCH.

## 3 Configuration and Control

This chapter details the mechanism for configuring, enabling and controlling the operation of RTIT. It is intended for developers who are writing software to support RTIT operation, whether in the OS/VMM or in the debug controller. This section can also be used as a reference for programming the relevant RTIT MSRs.

### 3.1 Enumeration

For Intel<sup>®</sup> Atom<sup>™</sup> processors, RTIT is not architectural and is therefore not enumerated in any way. To determine if the processor does support RTIT, the user can verify the Family, Model, and Stepping, and then use a try-accept to test for RTIT functionality.

## 3.2 RTIT accessibility

RTIT is configured via model-specific registers (MSRs). These can be controlled through either JTAG or ring-0 software. For details about JTAG access, please contact your Intel sales representative.

## 3.3 CPU Control and Model-Specific Registers

#### 3.3.1 General MSR notes for RTIT

All RTIT MSRs are described below, and are duplicated per logical processor. **Until the RTIT\_CTL MSR (0x768)** has been read any attempt to write any RTIT MSR, or read any RTIT MSR other than RTIT\_CTL, will result in a #GP fault.

For all RTIT MSRs, any MSR write that attempts to change (which usually means 'set') bits marked reserved will cause a #GP fault. RTIT MSRs are not cleared by INIT.

## 3.3.2 RTIT\_CTL MSR

**Table 4: RTIT CTL Control Register**

| Bit     | Name        | Description                                                                                                                                                                                                                                                                               |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Trace_En    | Global Enable Disable                                                                                                                                                                                                                                                                     |

| 1       | Cycle_Acc   | 0 : Cycle Accurate Mode is Disabled 1: Cycle Accurate Mode is Enabled                                                                                                                                                                                                                     |

| 2       | OS          | 0: Indicates OS level COFI will not be traced 1: Indicates OS level COFI will be traced                                                                                                                                                                                                   |

| 3       | User        | Indicates USER level COFI will be traced     Indicates USER level COFI will not be traced                                                                                                                                                                                                 |

| 4       | STS_on_CR3  | Generates STS packet on CR3 changes                                                                                                                                                                                                                                                       |

| [6:5]   | Rsvd        | Reserved                                                                                                                                                                                                                                                                                  |

| 7       | CR3En       | 0: Disables CR3 Filtering 1: Enables CR3 Filtering                                                                                                                                                                                                                                        |

| 8       | Dest        | O: Force TraceStop to be written to address offset 0xC0. See details below.  1: No special treatment of TraceStop packet                                                                                                                                                                  |

| 9       | MTC_En      | 0: MTC packet generation disabled 1: Enabled                                                                                                                                                                                                                                              |

| 10      | STS_En      | 0: STS packet generation disabled 1: Enabled                                                                                                                                                                                                                                              |

| 11      | Cmprs_Ret   | Compresses Return address                                                                                                                                                                                                                                                                 |

| 12      | Less_Pkts   | Generate less packets to improve bandwidth                                                                                                                                                                                                                                                |

| 13      | TraceActive | This is another overall RTIT valid bit which needs to be set for TriggerEnable to be 1 (just like RTIT_CTL.Trace_En). It is different from Trace_En in that it can be cleared by the TraceStop action. An MSR write that clears TraceActive should not cause a TraceStop packet, however. |

| [15:14] | MTC_Range   | Defines TSC granularity 00:TSC[14:7] 01:TSC[16:9] 02:TSC[18:11] 03:TSC[20:13]                                                                                                                                                                                                             |

| [31:16] | Reserved    | Reserved                                                                                                                                                                                                                                                                                  |

RTIT\_CTL [0]: Trace\_En

Trace\_En globally turns on or off the RTIT architecture. The reset value of Trace\_En is 0, disabling RTIT by default.

It is recommended that software set Trace\_En before setting TraceActive (below) when enabling tracing. Similarly, software should clear TraceActive before clearing Trace\_En when disabling tracing. If both Trace\_En and TraceActive transition 0->1 or 1->0 in the same WRMSR, undefined behavior may result.

RTIT\_CTL [1]: CYCLE\_ACC

CYCLE\_ACC enables or disables the cycle accurate mode of RTIT COFI tracing. When set (1'b1), a cycle count packet is appended to all outbound RTIT traffic with the exception of the PSB packet.

RTIT\_CTL [2]: OS

The OS bit is used to indicate that whether CPL0 code (usually OS code) should be traced. See  $\underline{2.4.1}$ . When this bit is cleared and the current CPL is 0, then the ContextEn will be 0 (which disables many things, including COFI packets).

RTIT\_CTL [3]: USER

The USER bit is used to indicate whether CPL1, CPL2, and CPL3 code (usually application code) should be traced or not. See  $\underline{2.4.1}$ . When this bit is cleared and the current CPL is 1, 2 or 3 (>0), then the ContextEn will be 0 (which disables many things including COFI packets).

RTIT CTL [4]: STS on CR3

This bit being set will cause Super Time Synch Packets to be sent out on MOV CR3 operations RTIT\_CTL [6:5]: Reserved.

RTIT\_CTL [7]: CR3En

When this bit is set, CR3 filtering is enabled and ContextEn will be zero if the CR3 value does not matches what is in RTIT\_CR3\_MATCH MSR. When ContextEn is 0, COFI packets are not generated.

When this bit is cleared, the CR3 value RTIT\_CR3\_MATCH do not affect ContextEn. This behavior is described in more detail in the "Tracing one app (CR3 filtering)" section.

RTIT\_CTL [8]: Dest

Controls treatment of the TraceStop packet. When cleared, the write of the TraceStop packet will force the lower 8 bits of the write address to 0xC0. This should only be used when RTIT output is directed to dedicated trace hardware such as PTI, on SoCs that support such specialized TraceStop treatment.

When set, there is no special treatment of the TraceStop packet. This mode supports output to DRAM, or to dedicated trace hardware such as PTI.

RTIT\_CTL [9]: MTC\_En

Used to enable or disable the Mini Time Counter. See Mini Time Counter (MTC) Packet section for more details.

RTIT\_CTL[10]: STS\_En

Used to enable or disable Synch packet generation. A value of '1' enables STS packet generation, while a value of '0' disables STS packet generation.

RTIT\_CTL [11]: CMPRS\_RET

Setting this bit changes the behavior of indirect transfer packet generation. When set, near RET instructions may be compressed against the NLIP of the preceding call. See Indirect Transfer compression for returns (RET) section for more details.

RTIT\_CTL [12]: LESS\_PKTS

The LESS\_PKTS bit is used to decrease the number of packets generated and thereby decrease bandwidth demands. Please refer to the following table for a complete representation of which packets are inhibited when LESS\_PKTS is set. Enable Groups and Packet Generation.

RTIT\_CTL [13]: TraceActive

The TraceActive bit must be set before anything in RTIT occurs because it is part of TriggerEnable. Thus when TraceActive is 0, TriggerEnable is 0 (and RTIT is off). It is cleared by TraceStop action and is settable only by an MSR write (e.g. WRMSR).

As described in the Trace\_En section above, TraceActive should only be modified while Trace\_En is set.

RTIT\_CTL [15:14]: MTC Range

MTC Count allows the user to specify which bits of the TSC will become bit 15:8 of the MTC packet as follows:

| MTC Range | Resulting TSC in MTC packet |

|-----------|-----------------------------|

| 00        | TSC[14:7]                   |

| 01        | TSC[16:9]                   |

| 02        | TSC[18:11]                  |

| 03        | TSC[20:13]                  |

RTIT\_CTL[31:16] Reserved.

MSR writes to any reserved bits results in a #GPO fault.

MSR writes to RTIT\_CTL will cause an RTIT drain and will not end until that drain is completed and all RTIT stores are globally observed. This ensures that any changes to RTIT\_CTL are visible in memory by the time the MSR write completes. Thus, if software turns off RTIT by clearing TraceActive, it can count on fields like RTIT\_OFFSET to be correct and constant after the MSR write.

A write to RTIT\_CTL that causes RTIT\_STATUS[TriggerEn] to become set (meaning that RTIT\_CTL[Trace\_En] and RTIT\_CTL[TraceActive] are both set and one of them was not set before) will cause the PSB packet to be sent out.

An MSR write to RTIT\_CTL that causes PacketEn to become 0 (e.g. by clearing OS or USR or by setting CR3En) will cause a FUP.PGD packet to be generated. An MSR write that causes PacketEn to become 0 by clearing TraceActive or Trace\_En may not generate a FUP.PGD. See the FUP.PGD section for more details.

An MSR write to RTIT\_CTL that causes PacketEn to become 1 will cause a FUP.PGE packet to be sent. The MSR address is 0x768. Reset value = 0.

## 3.3.3 RTIT\_STATUS MSR

RTIT\_STATUS can be read or written by software, but some bits (like ContextEn) are read-only and cannot be modified directly. Any writes that attempt to modify these read-only bits will have no effect on the value; but will not cause a #GP (they are not checked as reserved bits).

The MSR address is 0x769. Reset value=0.

RTIT STATUS [0]: FilterEn

This is the bit that is set upon entering a tracing region and cleared upon leaving a tracing region. It indicates that the IP is within the filtered regions (but can be manipulated). It is one of the three enables that make up Packet Enable.

RTIT STATUS [1]: ContextEn

This is the context enable bit. It is set when we are in the right context for tracing (e.g. correct CPL, CR3 value, not in VMM/SMM, etc.) It is one of the three enables that make up Packet Enable. It is read-only.

RTIT STATUS [2]: TriggerEn

This is the trigger enable bit. It is set when RTIT is overall enabled (RTIT\_CTL[Trace\_En] AND RTIT\_CTL[TraceActive]). It is one of the three enables that make up Packet Enable and is read-only.

RTIT STATUS [3]: Buffer\_Overflow

This bit indicates that there is currently a buffer overflow that is pending. Under certain circumstances, software may need to context-switch that information.

It is read/write and can be updated directly by the processor or by software through MSR writes.

RTIT STATUS [31:4]: RESERVED

MSR writes to any reserved bits result in a #GPO fault.

## 3.3.4 RTIT\_CNTP MSR

The MSR address is 0x76B. Reset Value: 22'b0

**Table 5: Cycle Counter**

| Bit        | Name     | Description                                  |

|------------|----------|----------------------------------------------|

| [ 21 : 0 ] | CNTP     | Count is a 22-bit incrementing counter value |

| [ 31 : 22] | Reserved | Reserved                                     |

CNTP is a 22-bit incrementing counter that counts up at a rate equal to the processor core clock. CNTP can be used to generate info on cycle count between packets in cycle accurate mode. More details of this counter are in the "Cycle Counter" section.

The counter value CNTP is reset back to 22'b0, when

- CPU reset occurs (warm or cold)

- CNTP overflows

- A packet is sent out with a cycle count (the current value of CNTP). This occurs on almost every packet sent out in Cycle Accurate mode (RTIT\_CTL[Cycle\_Acc]).

The RTIT hardware will attempt to send out a Periodic Cycle Count (FUP.PCC) Packet when the MSB (bit 21) of CNTP is set and it is in the appropriate mode. For more details, see the "Flow Update event: Packet Cycle Counter" section.

## 3.3.5 RTIT\_EVENTS MSR

The MSR address is 0x76C. Reset Value: 32'b0.

Table 6: RTIT Filter Enable

| Bit    | Name               | Description                                                                                  |

|--------|--------------------|----------------------------------------------------------------------------------------------|

| [2:0]  | Filter_Event_ID    | EventID which will control RTIT_STATUS.FilterEn (Filter Enable mode bit)                     |

| [5:3]  | TraceStop_Event_ID | EventID which will cause a TraceStop action (Stops Tracing by clearing RTIT_CTL.TraceActive) |

| [31:6] | Reserved           | Reserved                                                                                     |

RTIT\_EVENTS provides a means to conditionally enable RTIT based on the user defined events.

Filter Event\_ID allows the user to specify for which IPs FilterEnable should be set and for which it should be clear.

TraceStop Event\_ID allows the user to specify which IPs should cause the TraceStop action. The TraceStop action stops tracing (by clearing RTIT\_CTL.TraceActive it causes TriggerEn to become 0) and also causes a TraceStop packet to be generated.

Table 7. RTIT Event IDs

| EventID | Event Name       |

|---------|------------------|

| 000     | RANGE0           |

| 001     | RANGE1           |

| 010     | RANGE0    RANGE1 |

| 011     | Reserved         |

| 100     | Reserved         |

| 101     | Reserved         |

| 110     | Always off       |

| 111     | Always on        |

The table above describes the event IDs that can be programmed to either the Filter\_Event\_ID or the TraceStop\_Event\_ID. RANGE0 is defined as [RTIT\_LIP0..RTIT\_LIP2-1], while RANGE1 is defined as [RTIT\_LIP1..RTIT\_LIP3-1]. When RANGE0 and/or RANGE1 is used for one of these fields, this means that software that either executes an instruction at the base IP (specified by RTIT\_LIP0 or RTIT\_LIP1), or executes a taken branch or event whose target is within the range, will trigger the chosen behavior, be it FilterEn assertion to enable tracing, or TraceStop. Correspondingly, software that executes an instruction at the limit IP (RTIT\_LIP2 or RTIT\_LIP3), or a taken branch or event whose target is outside the range, will cause the CPU to detect that software has left the range.

This means that if RTIT is enabled from within RANGEO or RANGE1, the CPU will not trigger the FilterEn or TraceStop behavior until either the IP at the range base is executed, or until a taken branch or event lands within the range. If neither of these occurs before the software executes the IP at the limit of the range, no triggering will occur.

Note that behavior when RANGEO and RANGE1 overlap, or when the range base is greater than the range limit, is undefined. Software should avoid such scenarios, as undesirable behavior is likely to ensue.

## 3.3.6 RTIT\_LIPO-3 MSR

MSR numbers are 0x760, 0x761, 0x762, 0x763. Reset Value: 64'b0

Table 8: RTIT LIPO-3 Address Range Comparators

| Bit     | Name               | Description                                                                                             |

|---------|--------------------|---------------------------------------------------------------------------------------------------------|

| [47:0]  | LIP <i>N</i> _ADDR | Holds the LIP for comparison for TraceLIPN                                                              |

| [63:48] | LIP_SIGN_EXT       | Reads return the sign-extended value of bit 47 for each bit in this field. Writes to it have no effect. |

These MSRs serve to define the base and limit values for RANGE0 and RANGE1. See the RTIT\_EVENTS MSR for more details.

Note that reads of this MSR will return 0 for the LIP\_SIGN\_EXT field.

## 3.3.7 RTIT\_LAST\_LIP MSR

The MSR address is: 0x76E. Reset Value: 64'b0.

Table 9: RTIT Last LIP

| Bit     | Name            | Description                                   |

|---------|-----------------|-----------------------------------------------|

| [15:0]  | CMPRS_LIP_LOW   | Holds LIP[31:16] of the compressed LIP        |

| [31:16] | CMPRS_LIP_HIGH  | Holds LIP[47:32] of the compressed LIP        |

| [32]    | CMPRS_LIP_Valid | Indicates the compressed LIP values are valid |

| [63:33] | Reserved        | Reserved as 0                                 |

- LIP Compression compares the LIP being sent out with the last LIP sent out, so only 16-bit chunks which change are sent out. This further reduces the bandwidth requirements required by RTIT.

- LIP Compression applies to the Flow Update Packets (FUP) and Target IP Packet.

- o Compressed LIP High (CLH) is compared against LIP[47:32] of the packet being generated, while Compressed LIP Low is compared against LIP 31.

This entire MSR is cleared to 0 (reset value) when a PSB packet is generated and when a buffer overflow packet is generated.

## 3.3.8 RTIT\_CR3\_MATCH MSR

RTIT CR3 Match registers have the programmed CR3 value for trace filtering. The bits correspond to that defined in CR3 MSR. The MSR address is: 0x777. *Reset Value: 64'b0.*

**Table 10: RTIT CR3 Comparator**

| Bit     | Name      | Description                    |

|---------|-----------|--------------------------------|

| [63:36] | Reserved  | Reserved                       |

| [35:5]  | CR3[35:5] | Matches contents of CR3 [35:5] |

| [4:0]   | Reserved  | Reserved                       |

### 3.3.9 RTIT\_PKT\_CNT MSR

RTIT\_PKT\_CNT holds the number of packet bytes that have been generated since either RTIT was initially enabled, or a PSB packet was last sent out. It does not count packets that were dropped due to buffer overflow, since they were not 'generated'. The Pkt\_Cnt should also count the bytes in the PSB packet itself.

The MSR address is: 0x77C. Reset Value: 0x00020000.

**Table 11: RTIT Packet Bytes Counter**

| Bit     | Name     | Description                                                           |

|---------|----------|-----------------------------------------------------------------------|

| [13:0]  | Pkt_Cnt  | Contains the number of bytes of RTIT packets generated since last PSB |

| [15:14] | Reserved | Reserved                                                              |

| [17:16] | Pkt_Mask | Indicates what value of Pkt_Cnt should cause a PSB to be sent out     |

The Pkt\_Mask field indicates when a PSB packet will be sent (which will also clear the Pkt\_Cnt field).

| Pkt_Mask value | PSB sent out when this Pkt_Cnt bit is set                     |

|----------------|---------------------------------------------------------------|

| 0              | 11 (size of roughly 2047 bytes)                               |

| 1              | 12 (size of roughly 4095 bytes)                               |

| 2              | 13 (size of roughly 8191 bytes)                               |

| 3              | 14 (size of roughly 16383 bytes) <= Note that bit 14 does not |

|                | exist in this field; so consider it overflow of this field.   |

So when the Pkt\_Mask value is 0, then the PSB is sent out (and the Pkt\_Cnt field is cleared) whenever the Pkt\_Cnt value has a value with bit 11 set.

Usually, this would occur due to a packet being generated and causing the Pkt\_Cnt to be incremented to a value that has the 'monitored bit' set. So unless an MSR write is used to change Pkt\_Cnt, a Pkt\_Mask of 2 will mean that a PSB packet is generated approximately every 8095 (2<sup>13</sup>-1) packet bytes generated. The Pkt\_Cnt will also be reset to 0.

This is evaluated on writes to this MSR and after every packet is generated. Thus the PSB will not be generated in the middle of a packet, but may be generated between the packets generated by a single instruction.

For example: Pkt\_Cnt value is Oxffc and PKT\_Mask is 1 and a far transfer then occurs. It generates a FUP.FAR packet of 7 bytes (no compression was possible) and a FUP.TIP packet of 5 bytes (zero compression). The hardware detects the FUP.FAR would increase the Pkt\_Cnt to a value with bit 12 set (the monitored bit). As a result, it changes the Pkt\_Cnt to 0 (not 3, which is what would happen if we simply cleared bit 12 of the output). Then a PSB packet is generated (which is 9 bytes in size), and the Pkt\_Cnt is incremented to a value of 9. Then the FUP.TIP is sent out and the Pkt\_Cnt is incremented by 5 to a value of 0xE. The end result is the packets sent out are FUP.FAR, PSB, FUP.TIP and the Pkt\_Cnt goes from Oxffc to 0xE.

The PSB packet clears out the last LIP and last CALL NLIP compression; however, this does not take effect until the packet that caused the Pkt\_Cnt overflow is drained from the internal RTIT buffer into memory unit buffers. This means that some number of packets in the trace after the PSB packet may not have the last LIP and last CALL NLIP compression. On Intel® Atom™ processors, the LAST\_LIP and LAST\_CALL\_NLIP compression are guaranteed to be cleared no more than 4 packets after the PSB

#### 3.3.10 RTIT\_BASE\_ADDR MSR

The MSR address is: 0x770. Reset Value: 0xFDC00000.

**Table 12: RTIT Output Base Address**

| Bit     | Name           | Description                                   |

|---------|----------------|-----------------------------------------------|

| [5:0]   | Reserved       | Reserved as 0                                 |

| [35:6]  | Base_Phys_Addr | The physical base address for the RTIT output |

| [63:36] | Reserved       | Reserved as 0                                 |

RTIT\_BASE\_ADDR holds the physical base address where the RTIT packets will be written. The hardware uses RTIT\_BASE\_ADDR & RTIT\_LIMIT\_MASK as the output base address. This means that any bit which is set in both the base and mask MSR will be treated as if it was 0 in the base for all address calculations. For this reason, it is recommended to ensure that the RTIT BASE ADDR value is aligned to the size of the region (RTIT\_LIMIT\_MASK+1).

#### 3.3.11 RTIT\_LIMIT\_MASK MSR

The MSR address is: 0x771. Reset Value: 0x7F.

**Table 13: RTIT Output Limit Mask**

| Bit     | Name       | Description                                     |

|---------|------------|-------------------------------------------------|

| [5:0]   | Rsvd_as_1  | Reserved as 3F                                  |

| [21:6]  | Mask_Value | Mask value ANDed with RTIT write pointer offset |

| [31:22] | Reserved   | Reserved                                        |

The CPU will AND this value to the RTIT base offset to figure out when the RTIT base offset pointer need to wrap back to 0. Since this field is defined up to bit 21, an RTIT output buffer of up to 4 MB in size (2<sup>22</sup>) can be supported.

The hardware uses RTIT\_BASE\_ADDR & RTIT\_LIMIT\_MASK as the output base address. This means that any bit which is set in both the base and mask MSR will be treated as if it was 0 in the base for all address calculations. For this reason, it is recommended to ensure that the RTIT\_BASE\_ADDR value is aligned to the size of the region (RTIT\_LIMIT\_MASK+1).

#### 3.3.12 RTIT\_OFFSET MSR

The MSR address is: 0x772. Reset Value: 32'bh000.

**Table 14: RTIT Output Offset**

| Bit    | Name   | Description                                              |

|--------|--------|----------------------------------------------------------|

| [21:0] | Offset | Holds the value added to base to determine write address |

This MSR holds the offset within the current RTIT buffer. Adding it to the RTIT base will tell which physical address the next RTIT output byte should be sent to.

Since the value in this MSR will change as bytes drain from internal RTIT buffers, it can change even when no packets are being generated. To ensure that it is 'settled' an RTIT-draining operation should be done (like a WRMSR to RTIT\_CTL) between the last thing can generate a packet and an accesses to this MSR.

#### 3.3.13 RTIT\_TNT\_BUFF MSR

The TNT\_BUFF MSR should be initialized by writing a value of 1 instead of 0. Software should not attempt to write all zeroes to this MSR, as the hardware may not function correctly and may not generate the correct packets. A MSR write that attempts to write a value of all zeroes will cause a #GP.

The MSR address is 0x77D. This register is reset to a value of 1'b1.

**Table 15: RTIT TNT Packet Buffer**

| Bit   | Name | Description                      |

|-------|------|----------------------------------|

| [6:0] | TNT  | Corresponds to TNT packet byte0. |

All bits to the right of the MSB are valid when the MSB is set (1) (just like the actual TNT packet.)

RTIT\_TNT\_BUFF is a R/W MSR used to accumulate TNT packet bits as they are generated. Capturing the TNT bits for the next TNT packet in this MSR allows the processor to save and restore them in C6 events. There is also an MSR to allow software to change the value of this MSR on context switches.

As TNT bits shift in from the right, the valid bit (the first leading '1' i.e. MSB) is also left shifted. Once the valid bit (MSB/leading'1') is in bit position 6, a full TNT packet exists (and it should be soon sent out).

Once the full TNT packet is generated, the lower byte is sent out as a TNT packet (with cycle count added after it if Cycle Accurate mode is enabled), and this MSR is reset back to '1'. For more information on TNT packet generation and byte contents, please refer to the TNT packet description.

## 3.3.14 RTIT\_LAST\_CALL\_NLIP MSR

MSR write will cause a #GP on any attempt to set a reserved bit.

The MSR address is 0x76F. Reset Value: 32'bh000.

Table 16: RTIT Last Call NLIP

| Bit     | Name             | Description                                          |

|---------|------------------|------------------------------------------------------|

| [31:0]  | Call_NLIP[31:0]  | Stores the NLIP[31:0] of the last Call Instruction   |

| [47:32] | Call_NLIP[47:32] | Stores the NLIP [47:32] of the last Call Instruction |

| 48      | NLIP_Valid       | The stored NLIP[47:0] is valid                       |

The RTIT\_LAST\_CALL\_NLIP registers are used to store the NLIP of the last call retired. This is used for compressing the packet generation of indirect call/returns. For more details on the underlying architecture and a description of return compression please refer to the indirect transfer compression for returns section: "Indirect Transfer compression for returns (RET)".

This entire MSR is cleared to 0 (reset value) when a PSB packet is generated and when a buffer overflow packet is generated.

## 4 Trace Packets and Data Types

This chapter details the data generated by RTIT. It is useful for developers writing the interpretation code that will decode the data from RTIT and apply it to the traced source code. This chapter can also be used as a reference for the data structures and formats generated by RTIT.

## 4.1 Trace Packet Summary

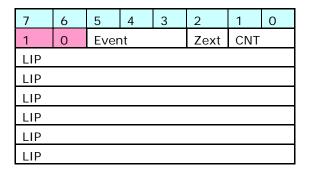

The following summarize the trace packet header.

|          | 7 | 6 | 5   | 4   | 3   | 2      | 1   | 0      |                          |  |

|----------|---|---|-----|-----|-----|--------|-----|--------|--------------------------|--|

|          | 0 | 1 | TNT | •   |     |        |     |        | 6 TNT                    |  |